Stability Improvement of GaN Power HEMT by a Multi-Functional Monolithic Protection Circuit

Abstract

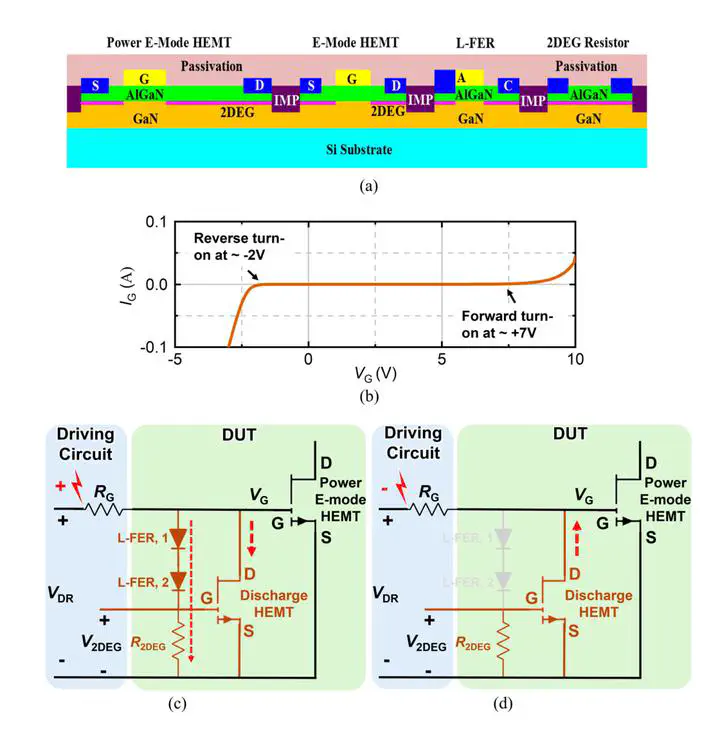

This work presents a gate electrostatic discharge (ESD) protection circuit monolithically integrated with the GaN power high-electron-mobility-transistor (HEMT). In addition to enhancing the gate robustness against the ESD event, this multifunctional circuit also improves the stability of on-resistance (RON) and threshold voltage (VTH) when power HEMT is under normal switching operations. Such improvement is enabled by clamping the HEMT’s negative gate bias (VG) at the off state, which is a critical cause of the RON and VTH instabilities in power p-gate GaN HEMTs. A circuit setup is deployed for the in situ monitoring of the dynamic RON and its evolution from the first switching cycle to the steady state. Under the off-state stress with negative VG and high drain bias (VD), the GaN HEMT without ESD circuit shows a drastic dynamic RON increase in the first tens of switching cycles. Such a phenomenon is fully suppressed by the ESD protection circuit. In addition, the longer-term stability of RON and VTH is tested under the prolonged stresses of VG and VD, in which the device with an ESD circuit shows superior stability. Physics-based technology-aided computer design simulation unveils the critical physics accounting for such stability improvement. These results reveal a new pathway to address the p-gate GaN HEMTs’ inherent instability while simultaneously boosting their gate robustness.